# Ingenic® RD4730\_PMP Reference Design

Hardware Manual

Version: 2.2

Date: May ,2007

Ingenic RD4730\_PMP Reference Design

**Hardware Manual**

Copyright © Ingenic Semiconductor Co. Ltd 2007. All rights reserved.

Release history

**Date** Revision Change May. 2007 2.2 First release

**Disclaimer**

This documentation is provided for use with Ingenic products. No license to Ingenic property rights is granted. Ingenic assumes no liability, provides no warranty either expressed or implied relating to the usage, or intellectual property right infringement except as provided for by Ingenic Terms and

Conditions of Sale.

Ingenic products are not designed for and should not be used in any medical or life sustaining or

supporting equipment.

All information in this document should be treated as preliminary. Ingenic may make changes to this document without notice. Anyone relying on this documentation should contact Ingenic for the

current documentation and errata.

Ingenic Semiconductor Co. Ltd

801C, Building E, Power Creative, No.1, ShangDi East Road,

Haidian District, Beijing 100085, China

Tel: 86-10-58851003

Fax: 86-10-58851005

Http://www.ingenic.cn

# Content

| 1 | Ov  | erview                                   | 1 |

|---|-----|------------------------------------------|---|

| 1 | .1  | Functions of RD4730_PMP                  | 1 |

| 1 | .2  | RD4730_PMP System Architecture           | 2 |

| 2 | На  | rdware Description                       | 3 |

| 2 | .1  | RD4730_PMP Layout                        | 3 |

| 2 | .2  | Power                                    | 3 |

| 2 | .3  | System Reset                             | 4 |

| 2 | .4  | Bootstrap                                | 4 |

| 2 | .5  | SDRAM                                    | 5 |

| 2 | .6  | LCD Interface                            | 5 |

| 2 | .7  | USB Interface                            | 6 |

| 2 | .8  | Audio System                             | 6 |

| 2 | .9  | Camera Interface                         | 6 |

| 2 | .10 | GSM+GPS Extension                        | 7 |

| 2 | .11 | IrDA                                     | 8 |

| 2 | .12 | Keypad Interface                         | 8 |

| 2 | .13 | MMC/SD Card                              | 8 |

| 2 | .14 | LCD Backlight                            | 8 |

| 2 | .15 | Debug Board Interface (RD4730_PMP_DEBUG) | 8 |

| 2 | .16 | System Status LED                        | 9 |

| 3 | Qu  | iick Start of RD4730 PMP1                | 1 |

# 1 Overview

Jz4730 is a multimedia application processor, which has a very high performance and low power 32-bit RISC engine. Jz4730 integrates various peripherals for embedded application, such as memory controller, USB1.1 host and device interface, Ethernet interface, LCD controller, AC'97/I2S interface, CMOS sensor interface, MMC/SD controller, SSI interface, I2C interface, UART, IrDA, GPIO, and so on.

The RD4730\_PMP is a reference design with Jz4730 addressing to consumer electronic equipment, that help engineer to quickly develop their own products in hardware and software. This design also provides flexible interface to extend other module.

With this reference design, there have richness development package include supporting WinCE™, CE-Linux™, and RTOS

#### 1.1 Functions of RD4730\_PMP

- High-performance processor Jz4730 running up to 400MHz, support CE-Linux and Windows CE.

- SDRAM: HY57561620-ECHT X 2 , 64MB。

- FLASH: NOR FLASH 2MB-8MB (optional) , NAND FLASH K9F1G08 128MB

- LCD: 480X272 4inch TFT with touch panel.

- Multimedia: I2s interface with AK4642, support MP3/MP4 player, MP4 decoder support 320X240 30f/s; stereo record with gain control; stereo line/headphone output with bass/treble control.

- CMOS sensor interface: 0.3 4 Mega Pixel.

- 5 key, can provide sound-button and soft power on/off; 5X5 keypad interface.

- USB1.1 Host / Device interface.

- 2-UART: support GPS+GSM module extension.

- MMC/SD extend interface: 256MB-2GB.

- Backlight control with PWM.

- Power on by RTC timer.

- Advanced power manager: Lithium-Ion battery charge; two low power mode of CPU sleep and

power off; quickly system power up in 1 minute; support RTC alarm and power up; very low

power consumption: less than 200MA in normal condition, Max. 350MA, and <=1MA in standby

mode; battery charging status indicator, and battery voltage monitor; auto in sleep mode when

no operation.</li>

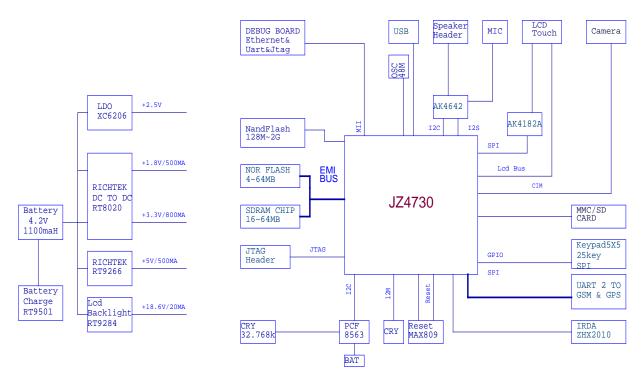

# 1.2 RD4730\_PMP System Architecture

Figure 1-1 RD4730\_PMP System Architecture

# 2 Hardware Description

In this section, will describe every hardware module of this design, please refer to the user's manual of Jz4730 first. For the others components, please refer to associated datasheet. For the details of the design, please refer to the schematic design.

# 2.1 RD4730\_PMP Layout

Figure 2-1shows the layout of main components and connectors.

Figure 2-1 RD4730\_PMP Layout

#### 2.2 Power

The RD4730\_PMP board is powered by 3.7V Lithium-lon battery, via header BT1. The button SW1, is power on/off switch. When in power off status, push SW1 will power on the board and the CPU should output 1 on PW\_O port immediately in order to keep the power. When the system is running, push

SW1 will assert a interrupt to CPU, then the software can clear PW\_O to power off the board after associated processing.

The main power chip is U7-RT8020, +3.3V, and +1.8V power supply and U16-RT9266 provides +5V power. The LED D1 indicates the status of +3.3V power.

The LCD backlight power is generated by U14 – RT9284, can provide about 20.8MA current. And U15 – XC6206 provides +2.5V power for LCD.

J8 is the external power supply jack, should connect with 6-7V 1A DC power adapter, together for battery charge. LED D7 indicates the charge status that light when charging, and inform to CPU via GPIO125 (can assert interrupt). The charge current is 550MA.

This board also can be powered with USB device port when connect to PC, and charge the battery together.

In this design there has a RTC chip U10 (PCF8563) powered by the coin cell battery B1, provides precision real time for system. When the system is in power off, it can provide time switch on the system via Q1.

### 2.3 System Reset

U8 (MIC811) makes up of the hardware reset circuit, provides system reset signal to all components when power on. SW2 is the manual reset button. And LED D2 can be used as status indicator when system software is running, that it connect to GPIO92.

#### 2.4 Bootstrap

There has two modes of bootstrap in this design:

- Bootstrap from NOR Flash U4.

- Bootstrap from NAND Flash U5.

When boot from NAND Flash, it can be from U5.

In this design, SW1 sets the bootstrap mode. When boot from U4, the setting of SW1 should be:

Table 2-1 describes the setting of SW1 when boot from NAND Flash.

#### Table 2-1 BOOT SETUP (SW3 ON=0)

| B_SEL0 | SW1.2 | Boot select input 0:                                                   |

|--------|-------|------------------------------------------------------------------------|

|        |       | NAND flash width when boot from it,0->8bit;1->16bit                    |

| B_SEL1 | SW1.3 | Boot_select input 1:                                                   |

|        |       | NAND flash page size when boot from it, 0->512B;1->2048B               |

| B_SEL2 | SW1.4 | Boot select input 2:                                                   |

|        |       | NAND flash address cycles when boot from it,0->low cycle;1->high cycle |

| B_SEL3 | SW1.1 | Boot select input 3:                                                   |

|        |       | 0->boot from ROM at CS0;1->boot from NAND flash device at CS3          |

For details about boot select setting, please refer to the Jz4730 Hardware Manual.

#### 2.5 SDRAM

This board has 64MB SDRAM, consist of two chips – U2 and U3, 4Banks X 4M X 16Bit.

#### 2.6 LCD Interface

J13 is the LCD interface, that can directly connect to SAMSUNG™ LTP400WQ-F02 LCD with touch panel. Or extend to connect to other LCD panel. Table 2-2 lists the signals definition of J13.

Table 2-1 LCD Interface (J13) Signals Definition

| Pin Number | Signal     | Pin Number | Signal    |

|------------|------------|------------|-----------|

| 1          | GND        | 2          | GND       |

| 3          | +2.5V      | 4          | +2.5V     |

| 5          | LCD_SPL    | 6          | LCD_CLS   |

| 7          | LCD_PS     | 8          | LCD_D11   |

| 9          | LCD_DD12   | 10         | LCD_DD13  |

| 11         | LCD_DD14   | 12         | LCD_DD15  |

| 13         | GND        | 14         | GND       |

| 15         | LCD_DD5    | 16         | LCD_DD6   |

| 17         | LCD_DD7    | 18         | LCD_DD8   |

| 19         | LCD_DD9    | 20         | LCD_DD10  |

| 21         | GND        | 22         | GND       |

| 23         | PWM0       | 24         | LCD_DD0   |

| 25         | LCD_D1     | 26         | LCD_D2    |

| 27         | LCD_D3     | 28         | LCD_D4    |

| 29         | GND        | 30         | LCD_PCLK  |

| 31         | DISP_OFF_N | 32         | LCD_HSYNC |

| 33         | LCD_VSYNC  | 34         | LCD_DE    |

| 35         | LCD_3.3V   | 36         | LCD_REV   |

| 37 | GND   | 38 | GND   |

|----|-------|----|-------|

| 39 | TSX+  | 40 | TSY+  |

| 41 | TSX-  | 42 | TSY-  |

| 43 | GND   | 44 | GND   |

| 45 | GND   | 46 | VLED- |

| 47 | VLED+ | 48 | GND   |

| 49 | GND   | 50 | GND   |

In JP15, there has some special control signals for some LCD panel: 1-LCD\_SPL; 2-LCD\_CLS; 3-LCD\_PS; 4-LCD\_REV. For details please refer to Jz4730 User's Manual.

#### 2.7 USB Interface

There has one USB 1.1 host port J4, one USB 1.1 device port J3. The source of USB clock (48MHz) can be external on board, or internal in Jz4730.

#### 2.8 Audio System

The audio system of this design, consist of I2S audio Codec AK4642EN, MIC-in jack J12, and output/headphone jack J11. There has two amplifier for external speaker connecting to the header SPK1. When plug a headphone in J11, the amplifier will be off.

The output volume, bass/treble boost and,

The audio system provides stereo record with gain control; stereo line/headphone output with bass/treble boost, and output volume control by software.

#### 2.9 Camera Interface

J2 is the CMOS sensor interface which directly connect with OV7649 module. Support maximum 400 Mega Pixel (2048X2048) camera module.

The signals of this interface are defined as below:

Table 2-2 Camera Interface (J2) Signals Definition

| Pin Number | Signal    | Pin Number | Signal    |

|------------|-----------|------------|-----------|

| 1          | GND       | 2          | CIM_HSYNC |

| 3          | CIM_VSYNC | 4          | PWDN      |

| 5          | CIM_PCLK  | 6          | +2.5V     |

| 7          | +3.3V     | 8          | I2C_SDA   |

| 9  | CLK_24MHz_CAM | 10 | I2C_SCK |

|----|---------------|----|---------|

| 11 | CIM_D0        | 12 | CIM_D1  |

| 13 | CIM_D2        | 14 | CIM_D3  |

| 15 | GND           | 16 | CIM_D4  |

| 17 | CIM_D5        | 18 | CIM_D6  |

| 19 | CIM_D7        | 20 | RESET   |

# 2.10 GSM+GPS Extension

In this design, there has a socket J5 for GSM and GPS module extension, that include: two UART port -0 and 3; audio in/out port; GSM control signals.

**Table 2-3 J5 Signals Definition**

| Pin Number | Signal     | GPIO Number |

|------------|------------|-------------|

| 1          | TXD0       |             |

| 2          | RXD0       |             |

| 3          | TXD3       |             |

| 4          | RXD3       |             |

| 5          | CTS3       |             |

| 6          | RTS3       |             |

| 7          | GSM_BOOT   | GPIO72      |

| 8          | GSM_RESET  | GPIO73      |

| 9          | GSM_EN     | GPIO74      |

| 10         | GSM_RING   | GPIO75      |

| 11         | GND        |             |

| 12         | MIC_GSM_IN |             |

| 13         | AGC_GND    |             |

| 14         | IO_3.3V    |             |

| 15         | GND        |             |

| 16         | GND        |             |

| 17         | BAT_V      |             |

| 18         | BAT_V      |             |

| 19         | MONO_IN    |             |

| 20         | +5V        |             |

#### 2.11 IrDA

RD4730\_PMP provides a IrDA transceiver U6, that can communication with SIR device, support maximum 4Mbps. And the UART 1 of Jz4730 can not be used in this design, since it has been set to IrDA mode.

# 2.12 Keypad Interface

There has a 5X5 matrix keypad interface J10, can connect a keypad as input device. GPIO99 – GPIO103, are defined as input with pull-up. GPIO104 – GPIO108 are defined as output controlled by software. For details, please refer to the table below.

**Table 2-4 J5 Signals Definition**

| Pin No. | Signal  | GPIO No. | Pin No. | Signal  | GPIO No. |

|---------|---------|----------|---------|---------|----------|

| 1       | Keyin1  | GPIO99   | 2       | Keyin2  | GPIO100  |

| 3       | Keyin3  | GPIO101  | 4       | Keyin4  | GPIO102  |

| 5       | Keyin5  | GPIO103  | 6       | Keyout1 | GPIO104  |

| 7       | Keyout2 | GPIO105  | 8       | Keyout3 | GPIO106  |

| 9       | Keyout4 | GPIO107  | 10      | Keyout5 | GPIO108  |

GPIO27, GPIO64, GPIO65, GPIO88, and GPIO89 have been pulled-up, used as normal key input. Marked as SW4 – SW8 in the design.

RD4730\_PMP also support PS/2 keyboard though header J6.

#### 2.13 MMC/SD Card

J9 is the MMC/SD card socket for extension memory, supports 32MB – 2GB MMC or SD card.

#### 2.14 LCD Backlight

By adjusting the PWM0 signal duty cycle, make the dimming control of LCD backlight consecutively and easily.

### 2.15 Debug Board Interface (RD4730\_PMP\_DEBUG)

In order to make the system debugging facility, there has a debug board – RD4730\_PMP\_DEBUG, connecting to the main board through head J1. It provides JTAG port – J3, UART3 port (DB9, RS-232)

- J4, and Ethernet port (RJ45) - J2.

# 2.16 System Status LED

There has three LED for system status indicator:

- LED D1 indicates the power status

- LED D2 connects to GPIO92, that controlled by software for system status

- LED D7 indicates the charge status that light when charging.

# 3 Quick Start of RD4730\_PMP

When you get the RD4730\_PMP board, it has been initialized with U-Boot, CELinux kernel and file system on the main board and SD card. Before power on the board, you should do the following step:

- Connecting the debug board RD4730\_PMP\_DEBUG

- Connecting serial port UART3 to a host PC as console (J6 on debug board), the configuration is 115200-8N1

- Connecting to your LAN

- Connecting a USB mouse to J4

- Connecting a battery to BT1, or use external DC power (6V, 1A)

#### Three manual have been used as:

- SW1: system power on/off and wakeup manual. Pushing it will switch on the board, long pushing will switch off then. When in sleep mode, pushing it will wake up the system.

- SW2: system reset manual.

- SW8: dimming control manual of LCD backlight.

After power on the board, there will be output on the console via serial port and LCD panel. After a moment, the demo of a QTOPIA application will be launched, letting you into a rich and colorful multimedia world.