# **1 External Memory Controller**

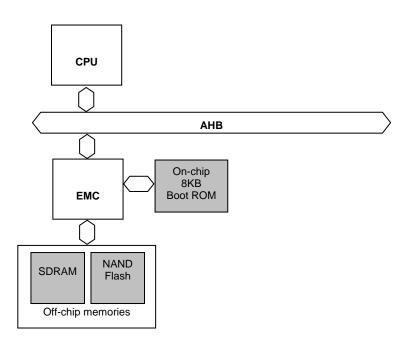

### 1.1 Overview

The External Memory Controller (EMC) divides the off-chip memory space and outputs control signals complying with specifications of various types of memory and bus interfaces. It enables the connection of static memory, NAND flash memory, synchronous DRAM, etc., to this processor.

- Static memory interface

- Direct interface to ROM, Burst ROM, SRAM and NOR Flash.

- Support 4 external chip selection CS4~1#. Each bank can be configured separately.

- The size and base address of static memory banks are programmable.

- Output of control signals allowing direct connection of memory to each bank. Write strobe setup time and hold time periods can be inserted in an access cycle to enable connection to low-speed memory

- Wait state insertion can be controlled by program.

- Wait insertion by WAIT pin.

- Automatic wait cycle insertion to prevent data bus collisions in case of consecutive memory accesses to different banks, or a read access followed by a write access to the same bank

- NAND flash interface

- Support on CS4~CS1, sharing with static memory bank4~bank1.

- Support most types of NAND flashes, including 8-bit and 16-bit bus width, 512B and 2KB page size. For 512B page size, 3 and 4 address cycles are supported. For 2KB page size, 4 and 5 address cycles are supported.

- Support read/erase/program NAND flash memory.

- Support boot from NAND flash.

- SDRAM Interface

- Support 2 chip selection DCS0# and DCS1#.

- Support both 32-bit and 16-bit bus width.

- Support both two-bank and four-bank type SDRAM.

- Support burst operation.

- Support both auto-refresh and self-refresh functions.

- The size and base address of each bank is configurable.

- Multiplexes row/column addresses according to SDRAM capacity

- Controls timing of SDRAM direct-connection control signals according to register setting

- Supports power-down mode to minimize the power consumption of SDRAM

- Support page mode

## 1.2 Pin Description

Following table list the EMC pins.

#### Table 1-1 EMC Pin Description

| Pin Name                 | I/O | Signal   | Description                                                    |

|--------------------------|-----|----------|----------------------------------------------------------------|

| Data Bus                 | I/O | D31 – D0 | Data I/O                                                       |

| Address bus              | 0   | A25–A0   | Address output                                                 |

| Static chip              | 0   | CS4~1#   | Chip select signal that indicates the static bank being        |

| select 4 ~ 1             |     |          | accessed                                                       |

| SDRAM chip               | 0   | DCS0#    | Chip select signal that indicates the SDRAM bank being         |

| select                   |     |          | accessed                                                       |

| SDRAM chip               | 0   | DCS1#    | Chip select signal that indicates the SDRAM bank being         |

| select                   |     |          | accessed                                                       |

| Read enable              | 0   | RD# /    | For Static memory read enable signal                           |

| Write enable             | 0   | WE# /    | Static memory write enable signal                              |

| Column<br>address strobe | 0   | CAS#     | SDRAM column address strobe signal                             |

| Row address<br>strobe    | 0   | RAS#     | SDRAM row address strobe signal                                |

| Read/write               | 0   | RD/WR#   | Data bus direction designation signal                          |

|                          |     |          | Also used as SDRAM write enable signal                         |

| Byte enable 0            | 0   | WE0# /   | For non-byte-control static memory, D7-0 write enable          |

|                          |     |          | signal,                                                        |

|                          |     | BE0# /   | For byte-control static memory, D7-0 selection signal          |

|                          |     | DQM0 /   | For SDRAM, D7–D0 selection signal                              |

| Byte enable 1            | 0   | WE1#/    | For non-byte-control static memory, D15-8 write enable signal  |

|                          |     | BE1# /   | For byte-control static memory, D15-8 selection signal         |

|                          |     | DQM1/    | For SDRAM, D15–D8 selection signal                             |

| Byte enable 2            | 0   | WE2# /   | For non-byte-control static memory, D23-16 write enable signal |

|                          |     | BE2# /   | For byte-control static memory, D23-16 selection signal        |

|                          |     | DQM2 /   | For SDRAM , D23–D16 selection signal                           |

| Byte enable 3            | 0   | WE3# /   | For static memory , D31-24 write enable signal                 |

|                          |     | BE3# /   | For byte-control static memory, D31-24 selection signal        |

|                          |     | DQM3     | For SDRAM, D31–D24 selection signal.                           |

| SDRAM Clock<br>enable    | 0   | CKE      | Enable the SDRAM clock                                         |

| SDRAM Clock              | 0   | СКО      | SDRAM clock                                                    |

| Wait                     | Ι   | Wait# /  | External wait state request signal for memory-like devices     |

| NAND flash               | 0   | FRE#     | NAND flash read enable signal                                  |

| read enable              |     |          | Ŭ Ŭ                                                            |

| NAND flash               | 0   | FWE#     | NAND flash write enable signal                                 |

| write enable             |     |          |                                                                |

| NAND flash               | 1   | FRB#     | Indicates NAND flash is ready or busy (When Nand flash         |

| ready/busy               |     |          | boot, GPC30 is used as FRB# of CS1#)                           |

XBurst JZ4750 program manual, Revision 1.0

2

Copyright® 2005-2010 Ingenic Semiconductor Co., Ltd. All rights reserved.

## 1.3 Physical Address Space Map

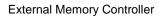

Both virtual spaces and physical spaces are 32-bit wide in this architecture. Virtual addresses are translated by MMU into physical address which is further divided into several partitions for static memory, SDRAM, and internal I/O.

| Start Address | End Address | Connectable Memory  | Capacity |

|---------------|-------------|---------------------|----------|

| H'0000 0000   | H'07FF FFF  | SDRAM space         | 128 MB   |

| H'0800 0000   | H'0FFF FFFF | Static memory space | 128 MB   |

| H'1000 0000   | H'13FF FFFF | Internal I/O space  | 64 MB    |

| H'1400 0000   | H'1BFF FFFF | Static memory space | 128MB    |

| H'1C00 0000   | H'1FBF FFFF | Un-used             | 60MB     |

| H'1FC0 0000   | H'1FC0 1FFF | On-chip boot ROM    | 8KB      |

| H'1FC0 1000   | H'1FFF FFFF | Un-used             | 4095KB   |

| H'2000 0000   | H'BFFF FFFF | SDRAM space         | 2944 MB  |

| H'D000 0000   | H'FFFF FFFF | Reserved space      | 512 MB   |

The base address and size of each memory banks are configurable. Software can re-configure these memory banks according to the actual connected memories. Following table lists the default configuration after reset.

| Table 1-3 Default Configuration of EN | MC Chip Select Signals |

|---------------------------------------|------------------------|

|---------------------------------------|------------------------|

| Chip-Selec          | Connected Memory     | Capacit | Memory    | Start       | End Address |

|---------------------|----------------------|---------|-----------|-------------|-------------|

| t Signal            |                      | у       | Width *1  | Address     |             |

| CS1#                | Static memory bank 1 | 8 MB    | 8, 16, 32 | H'1800 0000 | H'1BFF FFFF |

| CS2#                | Static memory bank 2 | 8 MB    | 8, 16, 32 | H'1400 0000 | H'17FFFFFFF |

| CS3#                | Static memory bank 3 | 8 MB    | 8, 16, 32 | H'0C00 0000 | H'0FFF FFFF |

| CS4#                | Static memory bank 4 | 8 MB    | 8, 16, 32 | H'0800 0000 | H'0BFF FFFF |

| DCS0# <sup>*3</sup> | SDRAM bank           | 128 MB  | 16, 32    | H'2000 0000 | H'27FF FFFF |

| DCS1# <sup>*3</sup> | SDRAM bank           | 128 MB  | 16, 32    | H'2800 0000 | H'2FFF FFFF |

Notes:

4

- 1) Data width of static memory banks can be configured to 8, 16 or 32 bits by software.

- The 8KB address space from H'1FC00000 to H'1FC01FFF in bank 0 is mapped to on-chip boot ROM. The other memory spaces in bank 0 are not used.

- To support large SDRAM space, EMC re-maps the physical address H'00000000-H07FFFFF to H'20000000-H'27FFFFFF. Software must configure the SDRAM base address by the re-mapped address.

### 1.4 Static Memory Interface

The static memory controller provides alueless interface SRAM's, ROMs а to (PROMs/EPROMs/FLASH), dual port memory, IO devices, and many other peripherals devices. It can directly control up to 4 devices using four chip select lines. Additional devices may be supported through external decoding of the address bus. The Device Controller shares the data and address busses with the SDRAM controller. Thus, only one memory subsection (SDRAM, memory, or IO) can be active at any time.

Each chip select can directly access memory or IO devices that are 8-bits, 16-bits, or 32-bits wide. Each device connected to a chip select line has 2 associated registers that control its operation and the access timing to the external device. The Static Memory Control Register SMCRn specifies various configurations for the device. The Static Memory Address Configuration Register SACRn specifies the base address and size for each device, enabling any device to be located anywhere in the physical address range.

The static memory interface includes the following signals:

- Four chip selects, CS4~1#

- Twenty-six address signals, A25-A0

- One read enable, RD#

- One write enable, WE#

- Four byte enable, BE3~1#

- One wait pin, WAIT#

The SMT field in SMCRn registers specifies the type of memory and BW field specifies the bus width. BOOT\_SEL[1:0] pin defines whether system boot from Nor or Nand flash and the page size when boot from Nand flash.

#### 1.4.1 Register Description

| Name  | Description                                            | RW | Reset Value | Address    | Access<br>Width |

|-------|--------------------------------------------------------|----|-------------|------------|-----------------|

| SMCR1 | Static memory control register 1                       | RW | 0x0FFF7700  | 0x13010014 | 32              |

| SMCR2 | Static memory control register 2                       | RW | 0x0FFF7700  | 0x13010018 | 32              |

| SMCR3 | Static memory control register 3                       | RW | 0x0FFF7700  | 0x1301001C | 32              |

| SMCR4 | Static memory control register 4                       | RW | 0x0FFF7700  | 0x13010020 | 32              |

| SACR1 | Static memory bank 1 address<br>configuration register | RW | 0x000018FC  | 0x13010034 | 32              |

| SACR2 | Static memory bank 2 address configuration register    | RW | 0x000016FE  | 0x13010038 | 32              |

| SACR3 | Static memory bank 3 address configuration register    | RW | 0x000014FE  | 0x1301003C | 32              |

| SACR4 | Static memory bank 4 address configuration register    | RW | 0x00000CFC  | 0x13010040 | 32              |

#### Table 1-4 Static Memory Interface Registers

#### 1.4.1.1 Static Memory Control Register (SMCR1~4)

SMCR1~4 are 32-bit read/write registers that contain control bits for static memory. On reset, SMCR1~4 are initialized to 0x0FFF7700.

| 10014 |

|-------|

| 10018 |

| 1001C |

| 10020 |

|       |

|       |

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

|     |   |   |   |   |   | ST | RV |   |   | TA | Ŵ |   |   | TE | 3P |   |   | - | ΓAH | ł |   |   | TA | S |   | BW      |   |   | BCM | BL  | SMT | OWI |

|-----|---|---|---|---|---|----|----|---|---|----|---|---|---|----|----|---|---|---|-----|---|---|---|----|---|---|---------|---|---|-----|-----|-----|-----|

| RST | 0 | 0 | 0 | 0 | 1 | 1  | 1  | 1 | 1 | 1  | 1 | 1 | 1 | 1  | 1  | 1 | 0 | 1 | 1   | 1 | 0 | 1 | 1  | 1 | ( | 0/x 0/x | 0 | 0 | 0   | 0 0 | ) ( | )   |

| Bits  | Name     | Description                                                               | RW |

|-------|----------|---------------------------------------------------------------------------|----|

| 31:28 | Reserved | Writes to these bits have no effect and always read as 0.                 | R  |

| 27:24 | STRV     | Static Memory Recovery Time: Its value is the number of idle cycles       | RW |

|       |          | (0~15 cycles) inserted between bus cycles when switching from one bank    |    |

|       |          | to another bank or between a read access to a write access in the same    |    |

|       |          | bank. Its initial value is 0xF (15 cycles).                               |    |

| 23:20 | TAW      | Access Wait Time: For normal memory, these bits specify the number of     | RW |

|       |          | wait cycles to be inserted in read strobe time. For burst ROM, these bits |    |

6

XBurst JZ4750 program manual, Revision 1.0

Copyright® 2005-2010 Ingenic Semiconductor Co., Ltd. All rights reserved.

| [     |          | specify the nu | mber of wait of | cycles to be inserted in first data read strobe  |    |

|-------|----------|----------------|-----------------|--------------------------------------------------|----|

|       |          | time.          |                 |                                                  |    |

|       |          |                | Wait cycle      | Wait# Pin                                        |    |

|       |          | 0000           | 0 cycle         | Ignored                                          |    |

|       |          | 0001           | 1 cycle         | Enabled                                          |    |

|       |          | 0010           | 2 cycles        | Enabled                                          |    |

|       |          | 0011           | 3 cycles        | Enabled                                          |    |

|       |          | 0100           | 4 cycles        | Enabled                                          |    |

|       |          | 0101           | 5 cycles        | Enabled                                          |    |

|       |          | 0110           | 6 cycles        | Enabled                                          |    |

|       |          | 0111           | 7 cycles        | Enabled                                          |    |

|       |          | 1000           | 8 cycles        | Enabled                                          |    |

|       |          | 1001           | 9 cycles        | Enabled                                          |    |

|       |          | 1010           | 10 cycles       | Enabled                                          |    |

|       |          | 1011           | 12 cycles       | Enabled                                          |    |

|       |          | 1100           | 15 cycles       | Enabled                                          |    |

|       |          | 1101           | 20 cycles       | Enabled                                          |    |

|       |          | 1110           | 25 cycles       | Enabled                                          |    |

|       |          | 1111           | 31 cycles       | Enabled (Initial Value)                          |    |

| 19:16 | TBP      |                |                 | t ROM, these bits specify the number of wait     | RW |

|       |          |                |                 | sequent access. For normal memory, these         |    |

|       |          |                |                 | vait cycles to be inserted in write strobe time. |    |

|       |          | TBP3~0         | Wait cycle      | Wait# Pin                                        |    |

|       |          | 0000           | 0 cycle         | Ignord                                           |    |

|       |          | 0001           | 1 cycle         | Enabled                                          |    |

|       |          | 0010           | 2 cycles        | Enabled                                          |    |

|       |          | 0011           | 3 cycles        | Enabled                                          |    |

|       |          | 0100           | 4 cycles        | Enabled                                          |    |

|       |          | 0101           | 5 cycles        | Enabled                                          |    |

|       |          | 0110           | 6 cycles        | Enabled                                          |    |

|       |          | 0111           | 7 cycles        | Enabled                                          |    |

|       |          | 1000           | 8 cycles        | Enabled                                          |    |

|       |          | 1001           | 9 cycles        | Enabled                                          |    |

|       |          | 1010           | 10 cycles       | Enabled                                          |    |

|       |          | 1011           | 12 cycles       | Enabled                                          |    |

|       |          | 1100           | 15 cycles       | Enabled                                          |    |

|       |          | 1101           | 20 cycles       | Enabled                                          |    |

|       |          | 1110           | 25 cycles       | Enabled                                          |    |

|       |          | 1111           | 31 cycles       | Enabled (Initial Value)                          |    |

| 15    | Reserved | Writes to thes | e bits have no  | effect and always read as 0.                     | R  |

| 14:12 | ТАН      | Address Hole   | d Time: Thes    | e bits specify the number of wait cycles to be   | RW |

|       |          | inserted from  | negation of re  | ad/write strobe to address.                      |    |

|       |          | TAH2~0         | Wait cycle      |                                                  |    |

XBurst JZ4750 program manual, Revision 1.0 Copyright® 2005-2010 Ingenic Semiconductor Co., Ltd. All rights reserved.

| r    |          |                 |                                                                   | 1  |

|------|----------|-----------------|-------------------------------------------------------------------|----|

|      |          | 000             | 0 cycle                                                           |    |

|      |          | 001             | 1 cycle                                                           |    |

|      |          | 010             | 2 cycles                                                          |    |

|      |          | 011             | 3 cycles                                                          |    |

|      |          | 100             | 4 cycles                                                          |    |

|      |          | 101             | 5 cycles                                                          |    |

|      |          | 110             | 6 cycles                                                          |    |

|      |          | 111             | 7 cycles (Initial Value)                                          |    |

| 11   | Reserved | Writes to the   | se bits have no effect and always read as 0.                      | R  |

| 10:8 | TAS      | Address Set     | <b>up Time:</b> These bits specify the number of wait cycles (0~7 | RW |

|      |          | cycles) to be   | inserted from address to assertion of read/write strobe.          |    |

|      |          | TAS2~0          | Wait cycle                                                        |    |

|      |          | 000             | 0 cycle                                                           |    |

|      |          | 001             | 1 cycle                                                           |    |

|      |          | 010             | 2 cycles                                                          |    |

|      |          | 011             | 3 cycles                                                          |    |

|      |          | 100             | 4 cycles                                                          |    |

|      |          | 101             | 5 cycles                                                          |    |

|      |          | 110             | 6 cycles                                                          |    |

|      |          | 111             | 7 cycles (Initial Value)                                          |    |

| 7:6  | BW       | Bus Width :     | These bits specify the bus width. this filed is writeable and     | RW |

|      |          | are initialized | to 0 by a reset.                                                  |    |

|      |          | BW1~0           | Bus Width                                                         |    |

|      |          | 00              | 8 bits (Initial Value)                                            |    |

|      |          | 01              | 16 bits                                                           |    |

|      |          | 10              | 32 bits                                                           |    |

|      |          | 11              | Reserved                                                          |    |

| 5:4  | Reserved | Writes to the   | se bits have no effect and always read as 0.                      | R  |

| 3    | BCM      | SRAM Byte       | Control Mode (BCM): When SRAM is connected; this bit              | RW |

|      |          | specifies the   | type of SRAM. This bit is only valid when SMT is set to 0.        |    |

|      |          | BCM             | Description                                                       |    |

|      |          | 0               | SRAM is set to normal mode (Initial Value)                        |    |

|      |          | 1               | SRAM is set to byte control mode                                  |    |

| 2:1  | BL       | Burst Lengt     | h (BL1, BL0): When Burst ROM is connected; these bits             |    |

|      |          | specify the n   | umber of burst in an access. These bits are only valid when       |    |

|      |          | SMT is set to   | 1.                                                                |    |

|      |          | BL1~0           | Burst Length                                                      |    |

|      |          | 00              | 4 consecutive accesses. Can be used with 8-, 16-, or              |    |

|      |          |                 | 32-bit bus width (Initial Value).                                 |    |

|      |          | 01              | 8 consecutive accesses. Can be used with 8-, 16-, or              |    |

|      |          | 01              |                                                                   |    |

|      |          | 01              | 32-bit bus width                                                  |    |

|      |          | 10              |                                                                   |    |

XBurst JZ4750 program manual, Revision 1.0 Copyright® 2005-2010 Ingenic Semiconductor Co., Ltd. All rights reserved.

|   |     | 11         | 32 consecutive accesses. Can only be used with 8-bit bus      |    |

|---|-----|------------|---------------------------------------------------------------|----|

|   |     |            | width                                                         |    |

| 0 | SMT | Static Mem | ory Type (SMT): This bit specifies the type of static memory. | RW |

|   |     | SMT        | Description                                                   |    |

|   |     | 0          | Normal Memory (Initial Value)                                 |    |

|   |     | 1          | Burst ROM                                                     |    |

#### 1.4.1.2 Static Bank Address Configuration Register (SACR1~4)

SACR1~4 defines the physical address for static memory bank 1 to 4, respectively. Each register contains a base address and a mask. When the following equation is met:

(physical\_address [31:24] & MASK<sub>n</sub>) == BASE<sub>n</sub>

The bank n is active. The *physical\_address* is address output on internal system bus. Static bank regions must be programmed so that each bank occupies a unique area of the physical address space. Bank 0 base address must be 0 because it's system boot address. Programming overlapping bank regions will result in unpredictable error. These registers are initialized by a reset.

|     | SACR1       |    |      |       |    |       |    |    |    |    |    |    |    |    |    |    |    |   |   |             |     |     |            | 0x1 | 301         | 00 | 34        |

|-----|-------------|----|------|-------|----|-------|----|----|----|----|----|----|----|----|----|----|----|---|---|-------------|-----|-----|------------|-----|-------------|----|-----------|

|     | SACR2       |    |      |       |    |       |    |    |    |    |    |    |    |    |    |    |    |   |   |             |     |     |            | 0x1 | <b>30</b> 1 | 00 | 38        |

|     | SACR3       |    |      |       |    |       |    |    |    |    |    |    |    |    |    |    |    |   |   | <b>0</b> x′ | 130 | 100 | 3 <b>C</b> | 0x1 | <b>30</b> 1 | 00 | <b>40</b> |

|     | SACR4       |    |      |       |    |       |    |    |    |    |    |    |    |    |    |    |    |   |   |             |     |     |            |     |             |    |           |

| Bit | 31 30 29 28 | 27 | 26 2 | 25 24 | 23 | 22 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7           | 6   | 5   | 4          | 3   | 2           | 1  | 0         |

|     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | BASE | MASK |  |

|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|------|------|--|

| RST | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |      |      |  |

#### Bits Name RW Description 31:16 Writes to these bits have no effect and read always as 0. Reserved R BASE RW 15:8 Address Base: Defines the base address of Static Bank n (n = 1 to 4). The initial values are: SACR1.BASE 0x18 SACR2.BASE 0x14 SACR3.BASE 0x0C SACR4.BASE 0x08 23:20 MASK RW Address Mask: Defines the mask of Static Bank n (n = 1 to 4). The initial values are: SACR1.MASK 0xFC SACR2.MASK 0xFC SACR3.MASK 0xFC SACR4.MASK 0xFC

#### 1.4.2 Example of Connection

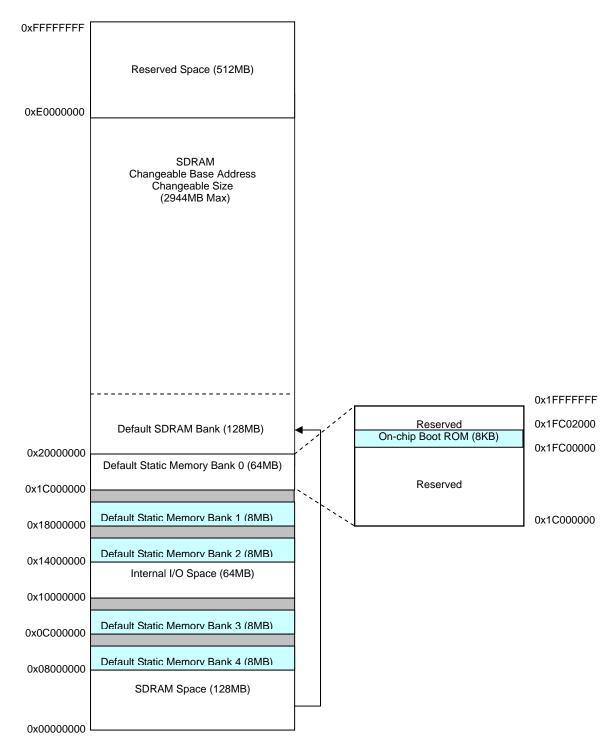

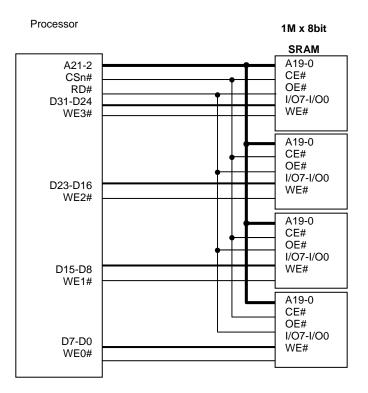

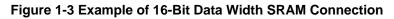

Following figures shows examples of connection to 32-, 16- and 8-bit data width normal memory.

Figure 1-2 Example of 32-Bit Data Width SRAM Connection

Figure 1-4 Example of 8-Bit Data Width SRAM Connection

#### 1.4.3 Basic Interface

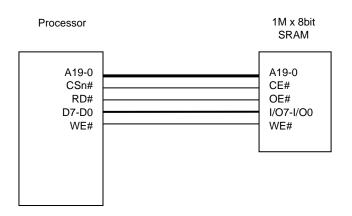

When SMT field in SMCRn (n = 1 to 4) is 0 and BCM field is 0, normal memory (non-burst ROM, Flash, normal SRAM or memory-like device) is connected to bank n. When bank n (n = 1 to 4) is accessed, CSn# is asserted as soon as address is output. In addition, the RD# signal, which can be used as OE#, and write control signals, WE0# to WE3#, are asserted.

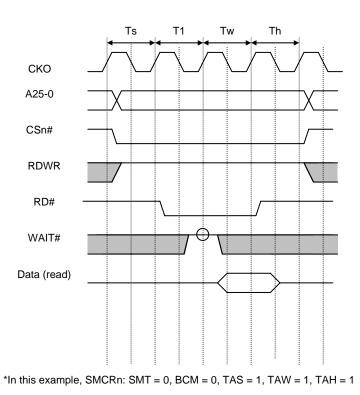

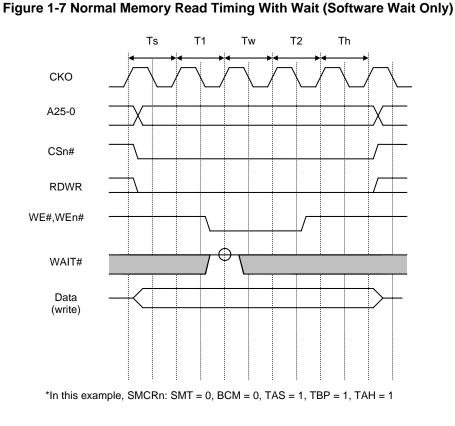

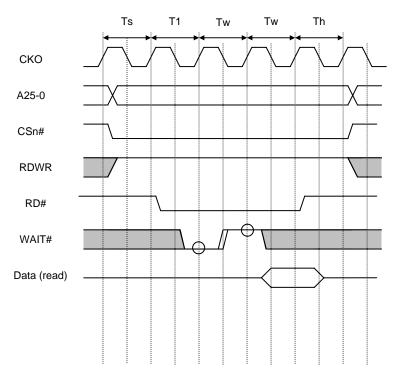

The TAS field in SMCRn is the latency from CSn# to read/write strobe. The TAW3 field is the delay time of RD# in read access. TBP3~0 field is the delay time of WE# and WEn# in write access. In addition, any number of waits can be inserted by means of the external pin (WAIT#). The TAH field is the latency from RD# and WEn# negation to CSn# negation, also the hold time to address and write data.

All kinds of normal memories (non-burst ROM, normal SRAM and Flash) have the same read and write timing. There are some requirements for writes to flash memory. Flash memory space must be un-cacheable and un-buffered. Writes must be exactly the width of the populated Flash devices on the data bus (no byte writes to a 32-bit bus or word writes to a 16-bit bus, and so on). Software is responsible for partitioning commands and data, and writing them out to Flash in the appropriate sequence.

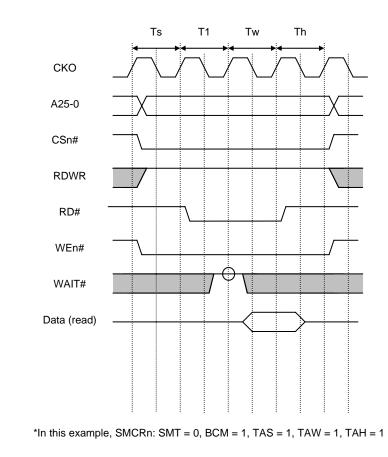

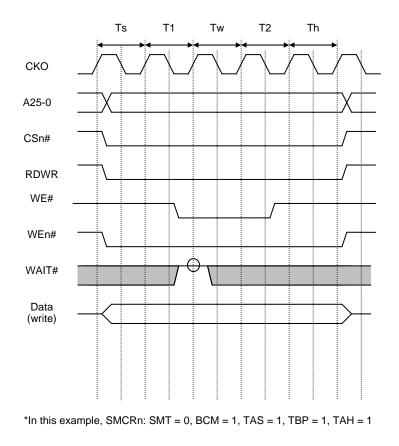

#### Glossary

- Th hold cycle

- Tw wait cycle

- Ts setup cycle

- T1 read inherent cycle or first write inherent cycle

- T2 last write inherent cycle

- Tb burst read inherent cycle

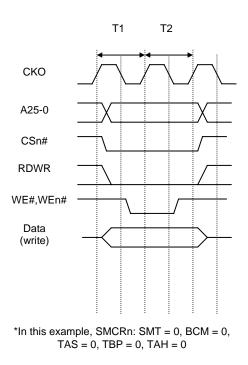

Following figures show the timing of normal memory. A no-wait read access is completed in one cycle and a no-wait write access is completed in two cycles. Therefore, there is no negation period in case of access at minimum pitch.

\*In this example, SMCRn:MT = 0, BCM = 0, TAS = 0, TAW = 0, TAH = 0

Figure 1-6 Basic Timing of Normal Memory Write

Figure 1-8 Normal Memory Write Timing With Wait (Software Wait Only)

\*In this example, SMCRn: SMT = 0, BCM = 0, TAS = 1, TAW = 1, TAH=1

#### Figure 1-9 Normal Memory Read Timing With Wait (Wait Cycle Insertion by WAIT# pin)

16

#### 1.4.4 Byte Control

The byte control SRAM interface is a memory interface that outputs a byte select strobe WEn# in both read and write bus cycles. It has 16 bit data pins, and can be directly connected to SRAM which has an upper byte select strobe and lower byte select strobe function such as UB# and LB#.

In read/write access, RD#/WE# is used as read/write strobe signal and WEn# are used as byte select signals.

Following figure shows an example of byte control SRAM connection to processor.

#### Figure 1-10 Example of 32-Bit Data Width Byte Control SRAM Connection

Following figures show examples of Byte Control SRAM timing.

Figure 1-11 Byte Control SRAM Read Timing

Figure 1-12 Byte Control SRAM Write Timing

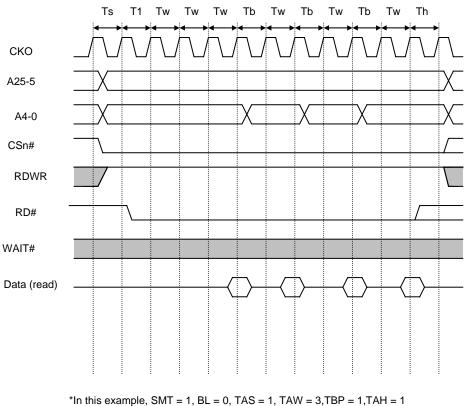

#### 1.4.5 Burst ROM Interface

Setting SMT to 1 in SMCRn allows burst ROM to be connected to bank n (n = 1 to 4). The burst ROM interface provides high-speed access to ROM that has a nibble access function. Basically, access is performed in the same way as for normal memory, but when the first cycle ends, only the address is changed before the next access is executed. When 8-bit burst ROM is connected, the number of consecutive accesses can be set as 4, 8, 16, or 32 with bits BL1~0. When 16-bit ROM is connected, 4, 8, or 16 can be set in the same way. When 32-bit ROM is connected, 4 or 8 can be set.

For burst ROM read, TAW sets the delay time from read strobe to the first data, TBP sets the delay time from consecutive address to data. Burst ROM writes have the same timing as normal memory except TAW instead of TBP is used to set the delay time of write strobe.

WAIT# pin sampling is always performed when one or more wait states are set.

Following figures show the timing of burst ROM.

In this example, SWT = T, BL = 0, TAS = T, TAW = 3, TBP = T, TAH = T

Figure 1-13 Burst ROM Read Timing (Software Wait Only)

20

### 1.5 NAND Flash Interface

NAND flash can be connected to static memory bank 4~ band 1. Both 8-bit and 16-bit NAND flashes are supported. A mechanism for booting from NAND flash is also supported.

#### 1.5.1 Register Description

#### Table 1-5 NAND Flash Interface Registers

| Name  | Description                        | RW | Reset Value | Address    | Access<br>Width |

|-------|------------------------------------|----|-------------|------------|-----------------|

| NFCSR | NAND flash control/status register | RW | 0x00000000  | 0x13010050 | 32              |

#### 1.5.1.1 NAND Flash Control/Status Register (NFCSR)

NFCSR is a 32-bit read/write register that is used to configure NAND flash. It is initialized by any reset.

|     | NFO | CSF | ł  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |       |      |       |      | <b>0</b> x | 130  | 10    | 050  |

|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|-------|------|-------|------|------------|------|-------|------|

| Bit | 31  | 30  | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7     | 6    | 5     | 4    | 3          | 2    | 1     | 0    |

|     |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   | NFCE4 | NFE4 | NFCE3 | NFE3 | NFCE2      | NFE2 | NFCE1 | NFE1 |

| RST | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0     | 0    | 0     | 0    | 0          | 0    | 0     | 0    |

| Bits   | Name      | Description                                                            | RW |

|--------|-----------|------------------------------------------------------------------------|----|

| 31:16  | Reserved  | Writes to these bits have no effect and read always as 0.              | R  |

| 1/3/5/ | FCEn      | NAND Flash FCE# Assertion Control : Controls the assertion of NAND     | RW |

| 7      | (n=1,2,3, | Flash FCEn#. When set, FCEn# is always asserted until this bit is      |    |

|        | 4)        | cleared. When the NAND flash require FCEn# to be asserted during read  |    |

|        |           | busy time, this bit should be set                                      |    |

|        |           | FCE Description                                                        |    |

|        |           | 0 FCEn# is asserted as normal static chip enable(Initial               |    |

|        |           | value)                                                                 |    |

|        |           | 1 FCEn# is always asserted                                             |    |

| 0/2/4/ | NFEn      | NAND Flash Enable: Specifies if NAND flash is connected to static bank | RW |

| 6      | (n=1,2,3, | n. When system is configured to boot from NAND flash, this bit is      |    |

|        | 4)        | initialized to 1.                                                      |    |

|        |           | NFE Description                                                        |    |

|        |           | 1. Static bank n is not used as NAND flash.                            |    |

|        |           | 2. Static bank n is used as NAND flash.                                |    |

#### 1.5.2 NAND Flash Boot Loader

To support boot from NAND flash, 8KB on-chip Boot ROM is implemented. Following figure illustrates the structure of NAND Flash Boot Loader.

Figure 1-14 Structure of NAND Flash Boot Loader

When system is configured to boot from NAND flash, after reset, the program in Boot ROM is executed and the program will copy the first 8K bytes of NAND flash to CACHE for further initialization.

Generally, the boot code will copy more NAND flash content to SDRAM. Then the main program will be executed on SDRAM.

#### 1.5.3 NAND Flash Operation

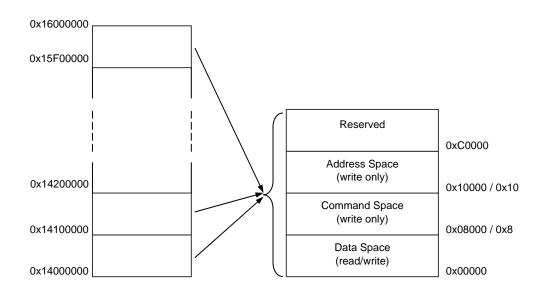

Set NFEn bit of NAND Flash Control/Status Register (NFCSR) will enable access to NAND flash. The partition of static bank n (n=1~4) is changed as following figure. Writes to any of address space will be translated to NAND flash address cycle. Writes to any of command space will be translated to NAND flash address cycle. Writes to address and command space, and these two partitions should be uncacheable. Reads and writes to any of data space will be translated to NAND flash data read/write cycle. DMA access to data space is supported to increase the speed of data read/write. The DMA access cannot exceed the page boundary (512 bytes or 2K bytes) of NAND flash.

Figure 1-15 Static Bank 2 Partition When NAND Flash is Used (an example)

The timing of NAND flash access is configured by SMCRn and is same as normal static memory timing, except that CSn# is controlled by NFCE bit NFCSR. CSn# is always asserted when NFCE is 1. When NFCE is 0, CSn# is asserted as normal static memory access.

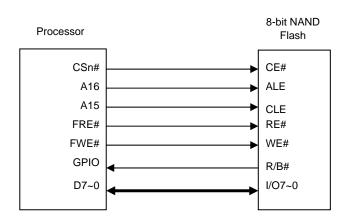

The control signals for direction connection of NAND flash are CSn#, FRE#, FWE#, FRB#(GPIO), A16 and A15. Following figure shows the connection between processor and NAND Flash.

Figure 1-16 Example of 8-bit NAND Flash Connection

Note:

When BCR.BSR is 0, A16 is connected to ALE, A15 is connected to CLE, software should write 0x10000 for address space and 0x8000 for command space;

When BCR.BSR is 1, A4 is connected to ALE, A3 is connected to CLE, software should write 0x10 for address space and 0x8 for command space.

## 1.6 SDRAM Interface

The SDRAM controller provides a glueless interface to industry standard SDRAM chip. The SDRAM controller provides two chip selects DCS0~1# supporting 16-bit or 32-bit wide SDRAM.

Both 2-bank and 4-bank SDRAM modules are supported. The bank select signals are always output from the A13 pin and A14 pin of processor.

The SDRAM interface includes the following signals:

- Two chip selects, DCS0#, DCS1#

- Four byte mask signals, DQM3~0#

- 15 multiplexed bank/row/column address signals, A14-A0

- One write enable, RD/WR#

- One column-address strobe CAS#

- One row-address strobe RAS#

- One clock enable CKE

- One clock CKO

The processor performs auto-refresh (CBR) during normal operation and supports self-refreshing SDRAM during sleep, hibernate, and frequency-change modes. An SDRAM power-down mode bit (DMCR[PDM]]) can be set so that the CKO and the clock-enable signal CKE to SDRAM are automatically deasserted whenever none of the corresponding banks is being accessed.

#### 1.6.1 Register Description

| Name  | Description                          | RW | Reset Value | Address      | Access<br>Width |

|-------|--------------------------------------|----|-------------|--------------|-----------------|

| DMCR  | DRAM control register                | RW | 0x0000 0000 | 0x13010080   | 32              |

| RTCSR | Refresh time control/status register | RW | 0x0000      | 0x13010084   | 16              |

| RTCNT | Refresh timer counter                | RW | 0x0000      | 0x13010088   | 16              |

| RTCOR | Refresh time constant register       | RW | 0x0000      | 0x1301008C   | 16              |

| DMAR1 | SDRAM bank 0 address                 | RW | 0x000020F8  | 0x13010090   | 32              |

|       | configuration register               |    |             |              |                 |

| DMAR2 | SDRAM bank 1 address                 | RW | 0x000028F8  | 0x13010094   | 32              |

|       | configuration register               |    |             |              |                 |

| SDMR  | Mode register of SDRAM bank          | W  |             | 0x1301-xxx   | 8               |

|       |                                      |    |             | (-: 4'b1xxx) |                 |

#### 1.6.1.1 SDRAM Control Register (DMCR)

DMCR is a 32-bit read/write register that specifies the timing, address multiplexing and refresh control of SDRAM. This enables direct connection of SDRAM without external circuits.

The DMCR is initialized to 0x00000000 by any resets. SDRAM bank should not be accessed until initialization is completed.

|     | DM | ICR |    |    |    |    |       |      |    |    |       |    |     |      |       |    |      |   |      |   |    |     |   |   |     |    |   | <b>0</b> x | 130 | 100 | 80 |

|-----|----|-----|----|----|----|----|-------|------|----|----|-------|----|-----|------|-------|----|------|---|------|---|----|-----|---|---|-----|----|---|------------|-----|-----|----|

| Bit | 31 | 30  | 29 | 28 | 27 | 26 | 25    | 24   | 23 | 22 | 21 20 | 19 | 18  | 17   | 16    | 15 | 14 1 | 3 | 12 1 | 1 | 10 | 9   | 8 | 7 | 6   | 5  | 4 | 3          | 2   | 1   | 0  |

|     | BW |     |    |    | CA |    | RMODE | RFSH |    |    | RA    | BA | MDA | EPIN | MBSEL | т  | RAS  |   | RCI  | D | ٦  | ГРС | ; |   | TR' | WL |   | ΓRC        | ;   | тс  | Ľ  |

| RST | 0  | 0   | 0  | 0  | 0  | 0  | 0     | 0    | 0  | 0  | 0 0   | 0  | 0   | 0    | 0     | 0  | 0 0  | ) | 0 (  | 0 | 0  | 0   | 0 | 0 | 0   | 0  | 0 | 0          | 0   | 0   | 0  |

| Bits  | Name     | Description   |                                                            | RW |

|-------|----------|---------------|------------------------------------------------------------|----|

| 31    | BW       | Specifies the | e data bus width of SDRAM                                  | RW |

|       |          | BW            | Description                                                |    |

|       |          | 0             | Data width is 32 bits (Initial value)                      |    |

|       |          | 1             | Data width is 16 bits                                      |    |

| 30:29 | Reserved | Writes to the | se bits have no effect and always read as 0.               | R  |

| 28:26 | CA       | Column Add    | dress Width: Specify the column address width of connected | RW |

|       |          | SDRAM chip    | ).                                                         |    |

|       |          | CA            | Description                                                |    |

26

XBurst JZ4750 program manual, Revision 1.0

Copyright® 2005-2010 Ingenic Semiconductor Co., Ltd. All rights reserved.

|       | [        | I             |                                                             | 1        |

|-------|----------|---------------|-------------------------------------------------------------|----------|

|       |          | 000           | 8 bits column address                                       |          |

|       |          | 001           | 9 bits column address                                       |          |

|       |          | 010           | 10 bits column address                                      |          |

|       |          | 011           | 11 bits column address                                      |          |

|       |          | 100           | 12 bits column address                                      |          |

|       |          | 101           | Reserved                                                    |          |

|       |          | 110           | Reserved                                                    |          |

|       |          | 111           | Reserved                                                    |          |

| 25    | RMODE    | Refresh Mod   | de.                                                         | RW       |

|       |          | RMODE         | Description                                                 |          |

|       |          | 0             | Auto-refresh                                                |          |

|       |          | 1             | Self-refresh                                                |          |

| 24    | RFSH     | Refresh Cor   | ntrol.                                                      | RW       |

|       |          | RFSH          | Description                                                 |          |

|       |          | 0             | No refresh is performed (Initial value)                     |          |

|       |          | 1             | Refresh is performed                                        |          |

| 23    | MRSET    | Mode Regis    | ter Set: Set when a SDRAM mode register setting is used.    | RW       |

|       |          | When this bi  | t is 0 and SDRAM mode register is written, a Pre-charge all |          |

|       |          | banks comm    | nand (PALL) is performed. When this bit is 1 and SDRAM      |          |

|       |          | mode regist   | er is written, a Mode Register Set command (MRS) is         |          |

|       |          | performed.    |                                                             |          |

|       |          | MRSET         | Description                                                 |          |

|       |          | 0             | All-bank pre-charge (Initial value)                         |          |

|       |          | 1             | Mode register setting                                       |          |

| 22    | Reserved | Writes to the | se bits have no effect and always read as 0.                | R        |

| 21:20 | RA       | Row Addres    | S Width: Specify the row address width of connected         | RW       |

|       |          | SDRAM.        |                                                             |          |

|       |          | RA            | Description                                                 |          |

|       |          | 00            | 11-bit row address (Initial value)                          |          |

|       |          | 01            | 12-bit row address                                          |          |

|       |          | 10            | 13-bit row address                                          |          |

|       |          | 11            | Reserved                                                    |          |

| 19    | BA       | Bank Addre    | ss Width: Specify the number of bank select signals for one | RW       |

|       |          | chip select.  |                                                             |          |

|       |          | BA            | Description                                                 |          |

|       |          | 0             | 1-bit bank address is used (2 banks each chip select)       |          |

|       |          | -             | (Initial value)                                             |          |

|       |          | 1             | 2-bit bank address is used (4 banks each chip select)       |          |

| 18    | PDM      | -             | <b>n Mode:</b> Set power-down mode. When power-down mode is | RW       |

|       |          |               | will be driven to power-down mode when it is not accessing  |          |

|       |          |               | ng. Clock supply to SDRAM will be stopped also.             |          |

|       |          | PDM           | Description                                                 |          |

|       |          | 0             | Non-power-down mode (Initial value)                         |          |

|       |          | 5             |                                                             | <u> </u> |

XBurst JZ4750 program manual, Revision 1.0 Copyright® 2005-2010 Ingenic Semiconductor Co., Ltd. All rights reserved.

|       |       | 1 Power-down mode                                                        |    |

|-------|-------|--------------------------------------------------------------------------|----|

| 17    | EPIN  | CKE Pin Control: Controls the level of CKE pin. Clearing this bit by     | RW |

|       |       | software causes a power-down command (if CKOEN of CPM is 1).             |    |

|       |       | Caution: after power-down command, all commands except                   |    |

|       |       | power-down-exit are prohibited. Setting this bit by software causes a    |    |

|       |       | power-down-exit command. Setting EPIN is a part of initializes procedure |    |

|       |       | for SDRAM.                                                               |    |

|       |       | EPIN Description                                                         |    |

|       |       | 0 CKE pin is deserted (Initial value)                                    |    |

|       |       | 1 CKE pin is asserted                                                    |    |

| 16    | MBSEL | Bank Select for Mode Register Load: It is used to distinguish to load    | RW |

|       |       | which bank Mode register.                                                |    |

|       |       |                                                                          |    |

|       |       | MBSEL Description                                                        |    |

|       |       | 0 Bank 0 (Initial value)                                                 |    |

|       |       | 1 Bank 1                                                                 |    |

| 15:13 | TRAS  | RAS Assertion Time: When synchronous DRAM is connected, these            | RW |

|       |       | bits set the minimum CKE negation time after self-refresh command is     |    |

|       |       | issued.                                                                  |    |

|       |       | TRAS Description                                                         |    |

|       |       | 000 4 (Initial value)                                                    |    |

|       |       | 001 5                                                                    |    |

|       |       | 010 6                                                                    |    |

|       |       | 011 7                                                                    |    |

|       |       | 100 8                                                                    |    |

|       |       | 101 9                                                                    |    |

|       |       | 110 10                                                                   |    |

|       |       | 111 11                                                                   |    |

| 12:11 | RCD   | RAS-CAS Delay: Set the SDRAM bank active-read/write command              | RW |

|       |       | delay time.                                                              |    |

|       |       | RCD Description                                                          |    |

|       |       | 00 1(Initial value)                                                      |    |

|       |       | 01 2                                                                     |    |

|       |       | 10 3                                                                     |    |

|       |       | 11 4                                                                     |    |

| 10:8  | TPC   | RAS Precharge Time: Specify the minimum number of cycles until the       | RW |

|       |       | next bank active command is output after precharging.                    |    |

|       |       | TPC Description                                                          |    |

|       |       | 000 1 cycle (Initial value)                                              |    |

|       |       | 001 2 cycles                                                             |    |

|       |       | 010 3 cycles                                                             |    |

|       |       | 011 4 cycles                                                             |    |

|       |       | 100 5 cycles                                                             |    |

XBurst JZ4750 program manual, Revision 1.0 Copyright® 2005-2010 Ingenic Semiconductor Co., Ltd. All rights reserved.

|     | 1        | 1                |                                                                |    |

|-----|----------|------------------|----------------------------------------------------------------|----|

|     |          | 101              | 6 cycles                                                       |    |

|     |          | 110              | 7 cycles                                                       |    |

|     |          | 111              | 8 cycles                                                       |    |

| 7   | Reserved | Writes to these  | bits have no effect and always read as 0.                      | R  |

| 6:5 | TRWL     | Write Prechar    | ge Time: Set the SDRAM write precharge delay time. In          | RW |

|     |          | auto-precharge   | e mode, they specify the time until the next bank active       |    |

|     |          | command is iss   | sued after a write cycle. After a write cycle, the next active |    |

|     |          | command is no    | ot issued for a period of TRWL + TPC.                          |    |

|     |          | TRWL             | Description                                                    |    |

|     |          | 00               | 1 cycle (Initial value)                                        |    |

|     |          | 01               | 2 cycles                                                       |    |

|     |          | 10               | 3 cycles                                                       |    |

|     |          | 11               | 4 cycles                                                       |    |

| 4:2 | TRC      | RAS Cycle Tin    | ne: For SDRAM, no bank active command is issued                | RW |

|     |          | during the perio | od TRC after an auto-refresh command. In self-refresh,         |    |

|     |          | these bits also  | specify the delay cycles to be inserted after CKE              |    |

|     |          | assertion.       |                                                                |    |

|     |          | TRC              | Description                                                    |    |

|     |          | 000              | 1 cycle (Initial value)                                        |    |

|     |          | 001              | 3 cycle                                                        |    |

|     |          | 010              | 5 cycle                                                        |    |

|     |          | 011              | 7 cycle                                                        |    |

|     |          | 100              | 9 cycle                                                        |    |

|     |          | 101              | 11 cycle                                                       |    |

|     |          | 110              | 13 cycle                                                       |    |

|     |          | 111              | 15 cycle                                                       |    |

| 1:0 | TCL      | CAS Latency:     | Specify the delay from read command to data becomes            | RW |

|     |          | available at the | e outputs.                                                     |    |

|     |          | TCL              | Description                                                    |    |

|     |          | 00               | Inhibit (Initial value)                                        |    |

|     |          | 01               | 2 cycles                                                       |    |

|     |          | 10               | 3 cycles                                                       |    |

|     |          | 11               | Inhibit                                                        |    |

#### 1.6.1.2 SDRAM Mode Register (SDMR)

SDMR is written to via the SDRAM address bus and is a 15-bit write-only register. It sets SDRAM mode for SDRAM bank. SDMR is undefined after a reset.

Write to the SDRAM mode register use the address bus rather than the data bus. If the value to be set is X and the SDMR address is Y, the value X is written in the SDRAM mode register by writing in address X + Y. Here Y is 0x8000, X is value for SDRAM configuration. For example X is 0x0022, random data is written to the address offset 0x8022, as a result, 0x0022 is written to the SDMR register. The range for value X is 0x0000 to 0x7FFF.

#### **SDMR**

#### 0x1301-000

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

#### SDRAM address

RST

30

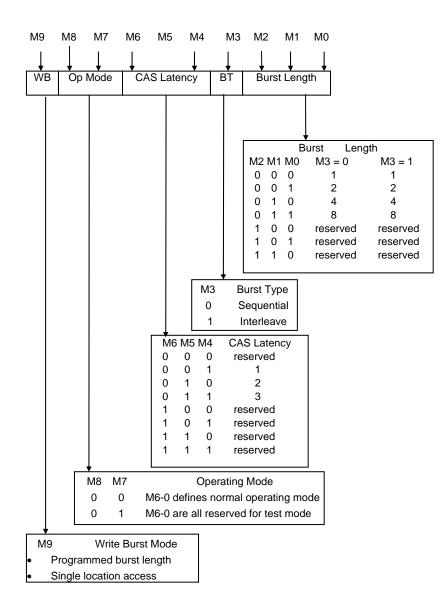

The Mode Register is used to define the specific mode of operation of the SDRAM. This definition includes the section of a burst length, a burst type, a CAS latency, an operating mode and a write burst mode, as shown in following figure.

For Mobile SDR, Extended Mode Register is used to define low power mode.

Figure 1-17 Synchronous DRAM Mode Register Configuration

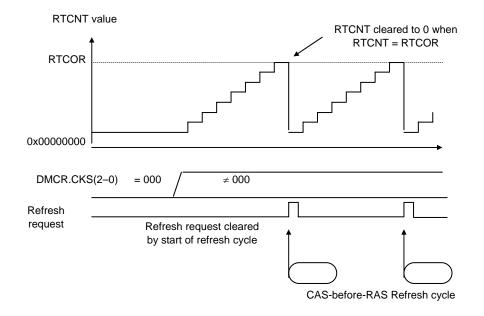

### 1.6.1.3 Refresh Timer Control/Status Register (RTCSR)

RTCSR is a 16-bit readable/writable register that specifies the refresh cycle and the status of RTCNT.

RTCSR is initialized to 0x0000 by a reset.

| RTSCR |          |    |    |    |    |     |     |   |     |      |   |   | <b>0</b> x | 130 | 100 | 84 |

|-------|----------|----|----|----|----|-----|-----|---|-----|------|---|---|------------|-----|-----|----|

| Bit   | 15       | 14 | 13 | 12 | 11 | 10  | 9   | 8 | 7   | 6    | 5 | 4 | 3          | 2   | 1   | 0  |

|       | Reserved |    |    |    |    | SRF | CMF | R | ese | erve | d | ( | CKS        | i   |     |    |

| RST   | 0        | 0  | 0  | 0  | 0  | 0   | 0   | 0 | 0   | 0    | 0 | 0 | 0          | 0   | 0   | 0  |

| Bits | Name     |                                                                       | Description                                              | RW |  |  |  |  |  |  |

|------|----------|-----------------------------------------------------------------------|----------------------------------------------------------|----|--|--|--|--|--|--|

| 15:9 | Reserved | These bits always read 0. Data written to these bits are ignored      |                                                          |    |  |  |  |  |  |  |

| 8    | SRF      | Self-refresh Flag (SRF): Status flag that indicates EMC already enter |                                                          |    |  |  |  |  |  |  |

|      |          | self-refresh sequ                                                     | ence                                                     |    |  |  |  |  |  |  |

|      |          | SRF De                                                                | scription                                                |    |  |  |  |  |  |  |

|      |          | 1) No self-                                                           | refresh (Initial value)                                  |    |  |  |  |  |  |  |

|      |          | Cle                                                                   | ar condition: When 0 is written, write 1 is ignored      |    |  |  |  |  |  |  |

|      |          | 2) EMC al                                                             | ready enter self-refresh sequence                        |    |  |  |  |  |  |  |

|      |          | Se                                                                    | t condition: when EMC enter self-refresh                 |    |  |  |  |  |  |  |

| 7    | CMF      | Compare-Match                                                         | Flag (CMF): Status flag that indicates a match between   | RW |  |  |  |  |  |  |

|      |          | the refresh timer                                                     | counter (RTCNT) and refresh time constant register       |    |  |  |  |  |  |  |

|      |          | (RTCOR) values                                                        | TCOR) values. Writes to 1 of this bit have no effect.    |    |  |  |  |  |  |  |

|      |          | CMF                                                                   | Description                                              |    |  |  |  |  |  |  |

|      |          | 0                                                                     | RTCNT and RTCOR values do not match (Initial value)      |    |  |  |  |  |  |  |

|      |          |                                                                       | Clear condition: When 0 is written                       |    |  |  |  |  |  |  |

|      |          | 1                                                                     | RTCNT and RTCOR values match                             |    |  |  |  |  |  |  |

|      |          |                                                                       | Set condition: When RTCNT = RTCOR                        |    |  |  |  |  |  |  |

| 2:0  | CKS      | Refresh Clock S                                                       | Select Bits: These bits select the clock input to RTCNT. | RW |  |  |  |  |  |  |

|      |          | The source clock                                                      | is the external bus clock (CKO). The RTCNT count         |    |  |  |  |  |  |  |

|      |          | clock is CKO divi                                                     | ded by the specified ratio.                              |    |  |  |  |  |  |  |

|      |          | CKS                                                                   | Description                                              |    |  |  |  |  |  |  |

|      |          | 000                                                                   | Disable clock input (Initial value)                      |    |  |  |  |  |  |  |

|      |          | 001                                                                   | Bus lock CKO/4                                           |    |  |  |  |  |  |  |

|      |          | 010                                                                   | CKO/16                                                   |    |  |  |  |  |  |  |

|      |          | 011                                                                   | CKO/64                                                   |    |  |  |  |  |  |  |

|      |          | 100                                                                   | CKO/256                                                  |    |  |  |  |  |  |  |

| L    |          | 101                                                                   | CKO/1024                                                 |    |  |  |  |  |  |  |

32

XBurst JZ4750 program manual, Revision 1.0

Copyright® 2005-2010 Ingenic Semiconductor Co., Ltd. All rights reserved.

| 110 | CKO/2048 |  |

|-----|----------|--|

| 111 | CKO/4096 |  |

#### 1.6.1.4 Refresh Timer Counter (RTCNT)

RTCNT is a 16-bit read/write register. RTCNT is a 16-bit counter that counts up with input clocks. The clock select bits (CKS2–CKS0) of RTCSR select the input clock. When the refresh bit (RFSH) of the memory control register (DMCR) is set to 1 and the refresh mode is set to auto-refresh, a memory refresh cycle starts when RTCNT matches RTCOR. RTCNT is initialized to 0x0000 by a reset.

| RTCNT | 0x1301008                             |

|-------|---------------------------------------|

| Bit   | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|       | Reserved                              |

| RST   | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 |

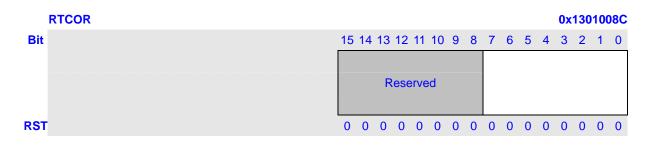

#### 1.6.2 Refresh Time Constant Register (RTCOR)

RTCOR is a 16-bit read/write register. The values of RTCOR and RTCNT (bottom 8 bits) are constantly compared. When the refresh bit (RFSH) of the memory control register (DMCR) is set to 1 and the refresh mode bit (RMODE) is set to auto-refresh, a memory refresh cycle starts when RTCNT matches RTCOR. RTCOR is initialized to 0x0000 by a reset.

#### **1.6.2.1** DRAM Bank Address Configuration Register (DMARn, n = 1, 2)

DMARn define the physical address for SDRAM bank0 or bank 1, respectively. Each register contains a base address and a mask. When the following equation is met:

$(physical\_address [31:24] \& MASK_n) == BASE_n$

The bank n is active. The *physical\_address* is address output on internal system bus. DRAM bank regions must be programmed so that each bank occupies a unique area of the physical address space. Programming overlapping bank regions will result in unpredictable error.

These registers are initialized by a reset.

|     | DMAR1    |       | 0x13010090 |       |    |    |      |       |      |      |    |    |    |    |    |    |    |   |   |   |   |   |    |    |   |   |   |

|-----|----------|-------|------------|-------|----|----|------|-------|------|------|----|----|----|----|----|----|----|---|---|---|---|---|----|----|---|---|---|

|     | DMAR2    |       | 0x13010094 |       |    |    |      |       |      |      |    |    |    |    |    |    |    |   |   |   |   |   |    |    |   |   |   |

| Bit | 31 30 29 | 28 27 | 26         | 25 24 | 23 | 22 | 21 2 | 20 19 | 9 18 | 8 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|     |          |       |            |       |    |    |      |       |      |      |    |    |    |    | BA | SE |    |   |   |   |   |   | MA | SK |   |   |   |

| RST |          |       |            |       |    |    |      |       |      |      |    | 0  | 0  | 1  | 0  | 0  | 0  | 0 | 0 | 1 | 1 | 1 | 1  | 1  | 0 | 0 | 0 |

| Bits  | Name     | Description                                                       | RW |

|-------|----------|-------------------------------------------------------------------|----|

| 31:16 | Reserved | Writes to these bits have no effect and read always as 0.         | R  |

| 15:8  | BASEn    | Address Base: Defines the base address of SDRAM Bank. The initial | RW |

|       |          | values are:                                                       |    |

|       |          | DMAR.BASE1 0x20                                                   |    |

|       |          | DMAR.BASE2 0x28                                                   |    |

| 23:20 | MASKn    | Address Mask: Defines the mask of SDRAM Bank.                     | RW |

|       |          | The initial values are:                                           |    |

|       |          | DMAR.MASK 0xF8                                                    |    |

#### 1.6.3 Example of Connection

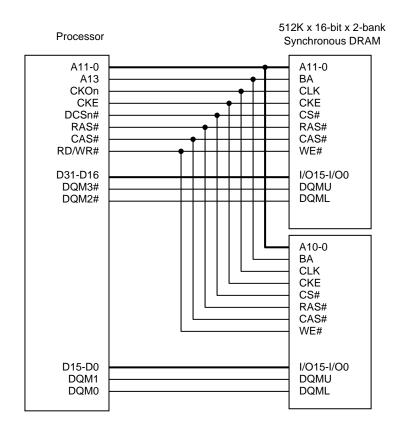

Following figure shows an example of connection of 512K x 16-bit x 2-bank SDRAM.

Figure 1-18 Example of Synchronous DRAM Chip Connection (1)

36

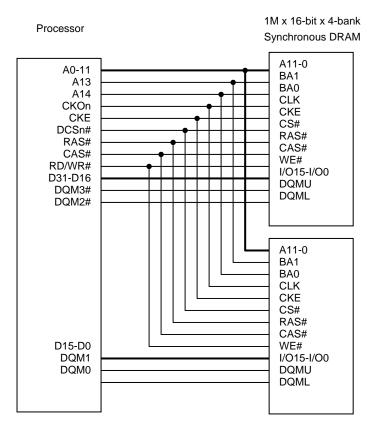

Following figure shows an example of connection of 1M x 16-bit x 4-bank synchronous DRAM.

Figure 1-19 Example of Synchronous DRAM Chip Connection (2)

## 1.6.4 Address Multiplexing

SDRAM can be connected without external multiplexing circuitry in accordance the address multiplex specification bits CA2~0, RA1~0 and BA in DMCR. Table 1-7 shows the relationship between the address multiplex specification bits and the bits output at the address pins.

A14-0 is used as SDRAM address. The original values are always output at these pins.

| CA2~0   | RA1~0   | Output<br>Timing | A0-A9, A10, A11, A12                 | A13 | A14 | Note |

|---------|---------|------------------|--------------------------------------|-----|-----|------|

| 8 bits  | 11 bits | Column           | A2-A11, L/H* <sup>1</sup> , A12, A13 | A21 | A22 | 3, 4 |

|         |         | Row              | A10-A22                              |     |     |      |

|         | 12 bits | Column           | A2-A11, L/H* <sup>1</sup> , A12, A13 | A22 | A23 | 3, 4 |

|         |         | Row              | A10-A22                              |     |     |      |

|         | 13 bits | Column           | A2-A11, L/H* <sup>1</sup> , A12, A13 | A23 | A24 | 3, 4 |

|         |         | Row              | A10-A22                              |     |     |      |

| 9 bits  | 11 bits | Column           | A2-A11, L/H* <sup>1</sup> , A12, A13 | A22 | A23 | 3, 4 |

|         |         | Row              | A11-A23                              |     |     |      |

|         | 12 bits | Column           | A2-A11, L/H* <sup>1</sup> , A12, A13 | A23 | A24 | 3, 4 |

|         |         | Row              | A11-A23                              |     |     |      |

|         | 13 bits | Column           | A2-A11, L/H* <sup>1</sup> , A12, A13 | A24 | A25 | 3, 4 |

|         |         | Row              | A11-A23                              |     |     |      |

| 10 bits | 11 bits | Column           | A2-A11, L/H* <sup>1</sup> , A12, A13 | A23 | A24 | 3, 4 |

|         |         | Row              | A12-A24                              |     |     |      |

|         | 12 bits | Column           | A2-A11, L/H* <sup>1</sup> , A12, A13 | A24 | A25 | 3, 4 |

|         |         | Row              | A12-A24                              |     |     |      |

|         | 13 bits | Column           | A2-A11, L/H* <sup>1</sup> , A12, A13 | A25 | A26 | 3, 4 |

|         |         | Row              | A12-A24                              |     |     |      |

| 11 bits | 11 bits | Column           | A2-A11, L/H* <sup>1</sup> , A12, A13 | A24 | A25 | 3, 4 |

|         |         | Row              | A13-A25,                             |     |     |      |

|         | 12 bits | Column           | A2-A11, L/H* <sup>1</sup> , A12, A13 | A25 | A26 | 3, 4 |

|         |         | Row              | A13-A25,                             |     |     |      |

|         | 13 bits | Column           | A2-A11, L/H* <sup>1</sup> , A12-A17  | A26 | A27 | 3, 4 |

|         |         | Row              | A13-A25,                             |     |     |      |

| 12 bits | 11 bits | Column           | A2-A11, L/H* <sup>1</sup> , A12, A13 | A25 | A26 | 3, 4 |

|         |         | Row              | A14-A26                              |     |     |      |

|         | 12 bits | Column           | A2-A11, L/H* <sup>1</sup> , A12, A13 | A26 | A27 | 3, 4 |

|         |         | Row              | A14-A26                              |     |     |      |

|         | 13 bits | Column           | A2-A11, L/H* <sup>1</sup> , A12, A13 | A27 | A28 | 3, 4 |

|         |         | Row              | A14-A26                              |     |     |      |

# Table 1-7 SDRAM Address Multiplexing (32-bit data width) \*4

#### Notes:

1) L/H is a bit used in the command specification; it is fixed at L or H according to the Access mode.

- 2) Bank address specification

- 3) If one bank select signal is used (BA = 0), take A13 as bank select signal. If two bank select signals are used (BA = 1), take A13 and A14 as bank select signals

- 4) The A0 to A14 in table head are output pins. The A2 to A28 in table body are physical address.

## 1.6.5 SDRAM Command

Commands for SDRAM are specified by RAS#, CAS#, RD/WR and special address signals. The processor accesses SDRAM by using the following subset of standard interface commands.

- 1. Mode Register Set (MRS)

- 2. Bank Activate (ACTV)

- 3. Read (READ)

- 4. Write (WRIT)

- 5. Burst Terminate

- 6. Precharge All Banks (PALL)

- 7. Auto-Refresh (CBR)

- 8. Enter Self-Refresh (SLFRSH)

- 9. No Operation (NOP)

| Command         |     |      |      | Proc   | essor Pi | ns           |     |      |

|-----------------|-----|------|------|--------|----------|--------------|-----|------|

|                 | CS# | RAS# | CAS# | RD/WR# | DQM      | A14-11, A9-0 | A10 | Note |

| INHIBIT         | Н   | Х    | Х    | Х      | Х        | Х            | Х   |      |

| NOP             | L   | н    | н    | Н      | Х        | Х            | Х   |      |

| MRS             | L   | L    | L    | L      | Х        | Op-Code      | -   |      |

| ACTV            | L   | L    | н    | Н      | Х        | Bank, Row    | Х   | 2    |

| READ            | L   | Н    | L    | Н      | L/H      | Bank, Col    | L   | 3    |

| WRIT            | L   | Н    | L    | L      | L/H      | Bank, Col    | L   | 3    |

| Burst Terminate | L   | Н    | н    | L      | Х        | Х            | Х   |      |

| PRE             | L   | L    | н    | L      | Х        | Bank         | L   |      |

| PALL            | L   | L    | н    | L      | Х        | Х            | Н   |      |

| CBR/SLFRSH      | L   | L    | L    | Н      | Х        | Х            | Х   | 4    |

## Table 1-8 SDRAM Command Encoding (Notes: 1)

#### Note:

- CKE is HIGH for all commands shown except SLFRSH

- A0-A12 provides row address, and A13-A14 determines which bank is active.

- A0-A9 provides column address, and A13-A14 determines which bank is being read from or written to.

- This command is CBR if CKE is HIGH, SLFRSH if CKE is LOW.

40

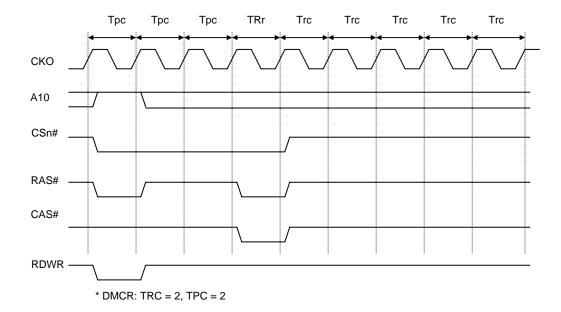

## 1.6.6 SDRAM Timing

The SDRAM bank function is used to support high-speed accesses to the same row address. As SDRAM is internally divided into two or four banks, it is possible to activate one row address in each bank.

When a de-active bank is accessed, an access is performed by issuing an ACTV command following by READ or WRIT command.

When an active bank is accessed and just hit the open row, an access is performed by issuing READ or WRIT command immediately without issuing an ACTV command.

When an active bank is accessed but hit a closed row, a PRE command is first issued to precharge the bank, then the access is performed by issuing an ACTV command followed by a READ or WRIT command.

There is a limit on Tras, the time for placing each bank in the active state. If there is no guarantee that there will not be a cache hit and another row address will be accessed within the period in which this value is maintained by program execution, it is necessary to set auto-refresh and set the refresh cycle to no more than the maximum value of Tras. In this way, it is possible to observe the restrictions on the maximum active state time for each bank. If auto-refresh is not used, measures must be taken in the program to ensure that the banks do not remain active for longer than the prescribed time.

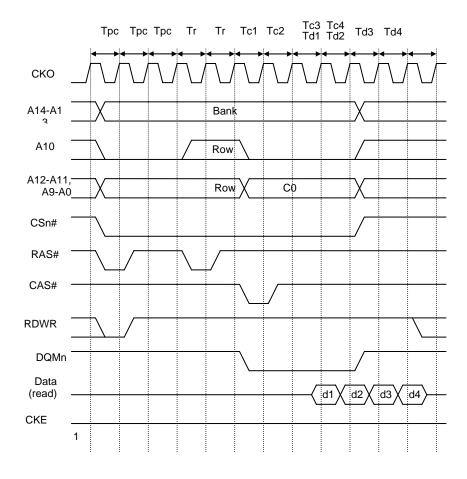

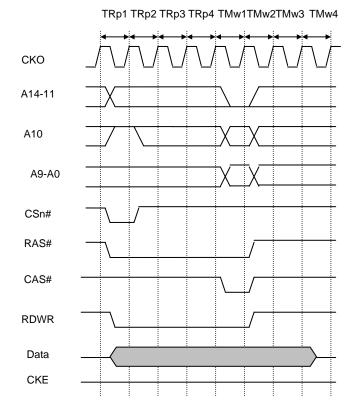

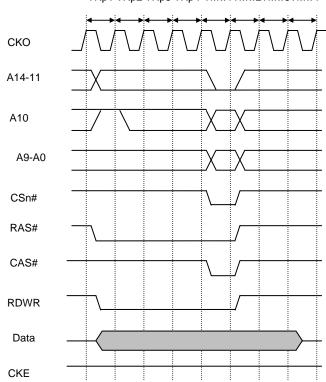

#### Glossary

Tr - row active cycle Trw - row active wait cycle Trwl - write latency cycle Tpc - precharge cycle TRr - refresh command cycle Trc - RAS cycle Trs1 – self refresh cycle 1 Trs2-self refresh cycle 2 Trs3-self refresh cycle 3 Trsw - self refresh wait cycle Tc1 – command cycle 1 Tc2 – command cycle 2 Tc3 - command cycle 3 Tc4 – command cycle 4 Tc5 – command cycle 5 Tc6 – command cycle 6 Tc7 – command cycle 7 Tc8 - command cycle 8

XBurst JZ4750 program manual, Revision 1.0

Copyright® 2005-2010 Ingenic Semiconductor Co., Ltd. All rights reserved.

- Td1 data cycle 1

- Td2 data cycle 2

- Td3 data cycle 3

- Td4 data cycle 4

- Td5 data cycle 5

- Td6 data cycle 6

- Td7 data cycle 7

- Td8 data cycle 8

- TRp1 precharge-all cycle 1

- TRp2 precharge-all cycle 2

- TRp3 precharge-all cycle 3

- TRp4 precharge-all cycle 4

- TMw1 mode register set cycle 1

- TMw2 mode register set cycle 2

- TMw3 mode register set cycle 3

- TMw4 mode register set cycle 4

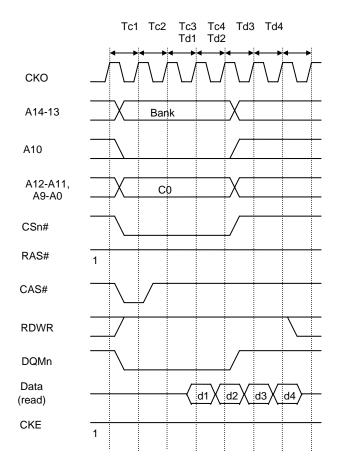

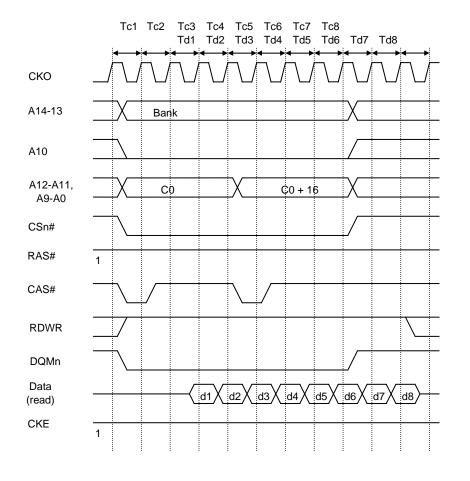

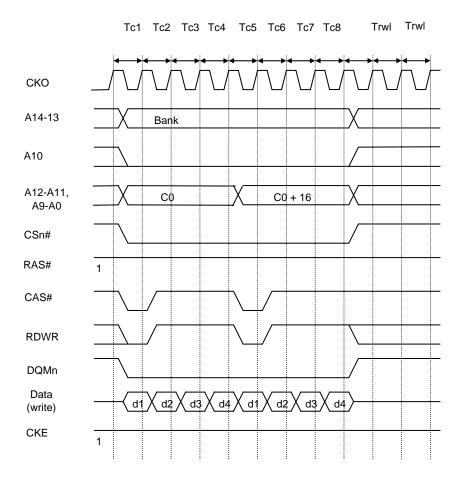

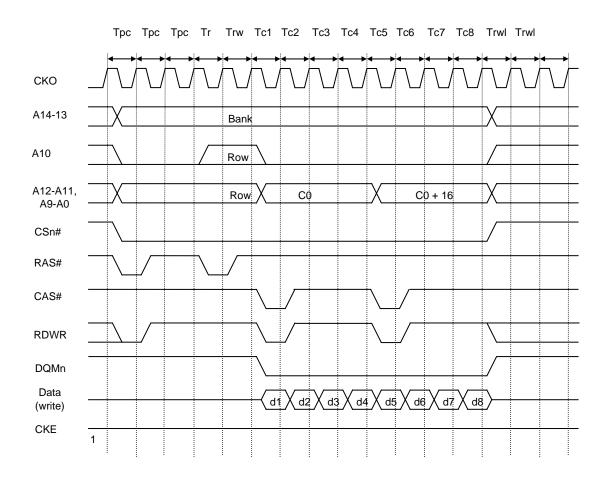

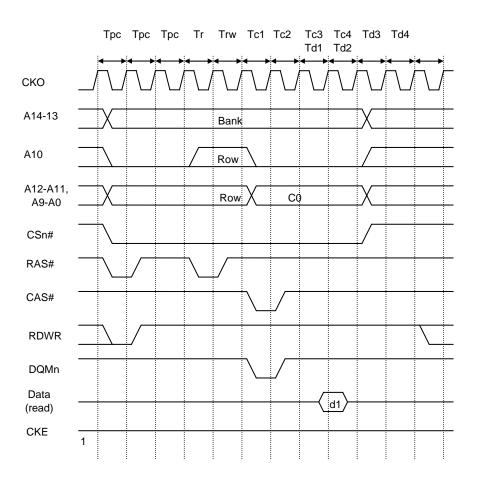

Following figures show the timing of 4-beat burst access, 8-beat burst access and single access.

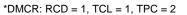

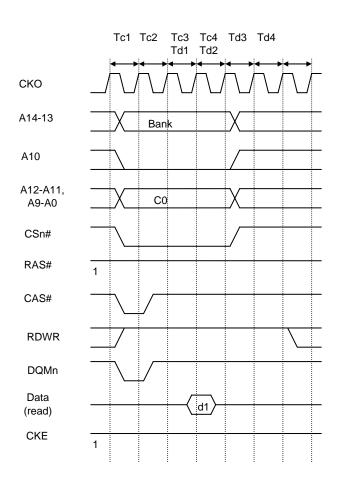

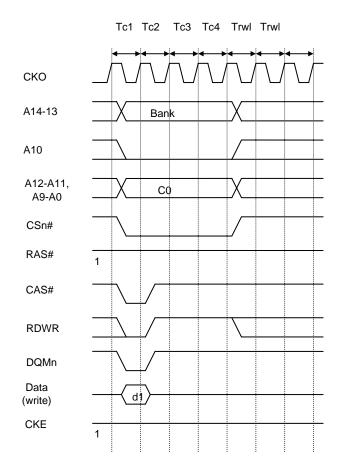

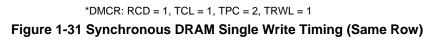

\*DMCR: RCD = 1, TCL = 1, TPC = 2

Figure 1-20 Synchronous DRAM 4-beat Burst Read Timing (Different Row)

Figure 1-21 Synchronous DRAM 4-beat Burst Read Timing (Same Row)

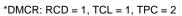

Tpc Tpc Tpc Tr Trw Tc1 Tc2 Tc3 Tc4 Trwl Trwl

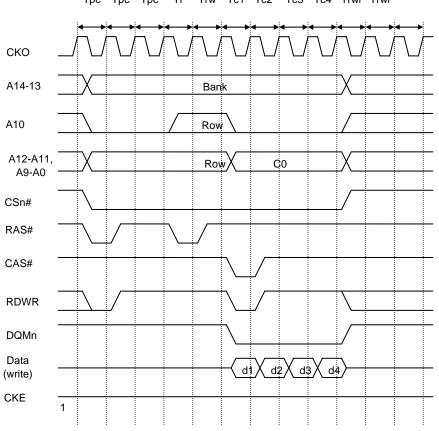

\*DMCR: RCD = 1, TCL = 1, TPC = 2, TRWL = 1

Figure 1-22 Synchronous DRAM 4-beat Burst Write Timing (Different Row)

46

君正 Ingenic

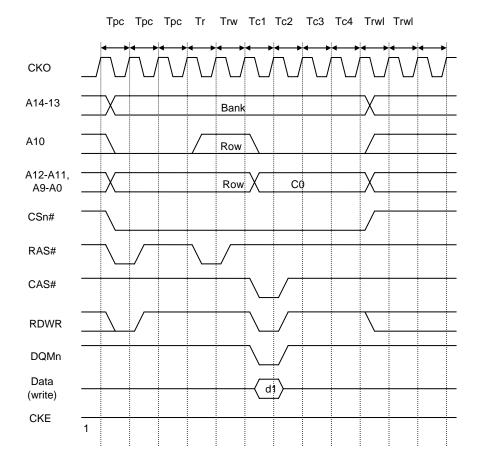

\*DMCR: RCD = 1, TCL = 1, TPC = 2, TRWL = 1

Figure 1-23 Synchronous DRAM 4-beat Burst Write Timing (Same Row)

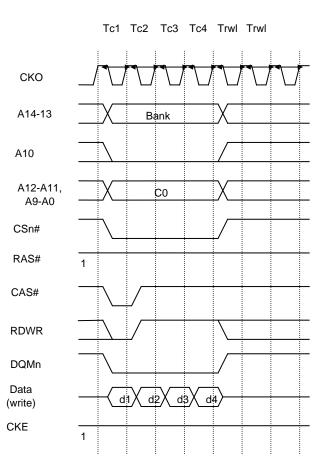

\*DMCR: RCD = 1, TCL = 1, TPC = 2

Figure 1-24 Synchronous DRAM 8-beat Burst Read Timing (Different Row)

48

君正 Ingenic

\*DMCR: RCD = 1, TCL = 1, TPC = 2

Figure 1-25 Synchronous DRAM 8-beat Burst Read Timing (Same Row)

\*DMCR: RCD = 1, TCL = 1, TPC = 2, TRWL = 1

Figure 1-26 Synchronous DRAM 8-beat Burst Write Timing (Same Row)

50

\*DMCR: RCD = 1, TCL = 1, TPC = 2, TRWL = 1

Figure 1-27 Synchronous DRAM 8-beat Burst Write Timing (Different Row)

\*DMCR: RCD = 1, TCL = 1, TPC = 2

Figure 1-28 Synchronous DRAM Single Read Timing (Different Row)

Figure 1-29 Synchronous DRAM Single Read Timing (Same Row)

52

\*DMCR: RCD = 1, TCL = 1, TPC = 2, TRWL = 1

Figure 1-30 Synchronous DRAM Single Write Timing (Different Row)

54

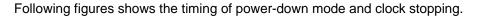

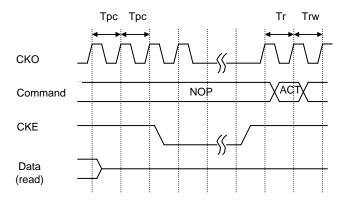

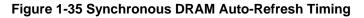

## 1.6.7 Power-Down Mode

The SDRAM power-down mode is supported to minimize the power consumption. CKE going to low level when SDRAM is idle/active state will drive SDRAM to precharge/active power-down mode. The clock supplies to SDRAM may be stopped also when CKE keep in low level more than two cycles. When a new access start or a refresh request, CKE is driven to high level and clock supplies is re-enabled. In power-down mode, clock of the accessed SDRAM bank pair is supplied. Clock of the other pair is stopped.

Figure 1-32 SDRAM Power-Down Mode Timing (CKO Stopped)